Respuesta corta :Estos son iguales.

Más detalles :Primero, vea esta publicación que está muy relacionada con su pregunta.

En este artículo dice:

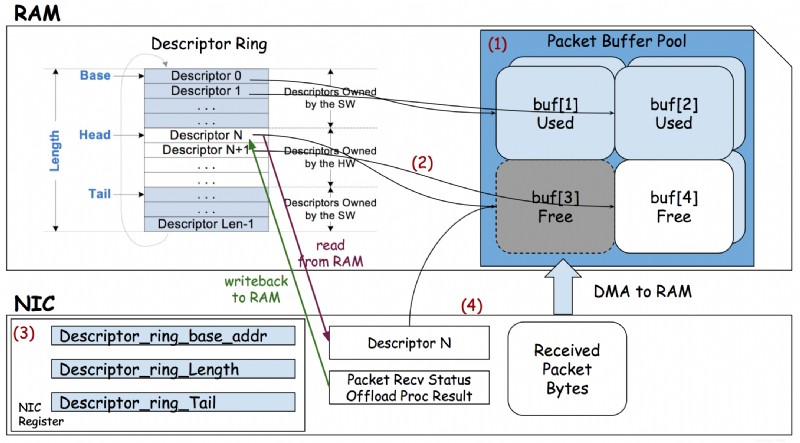

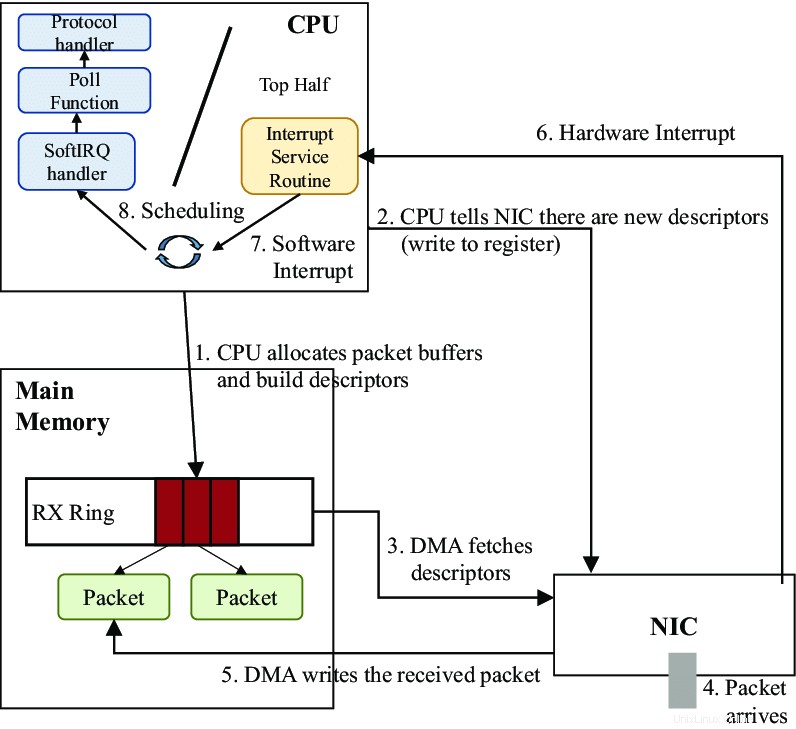

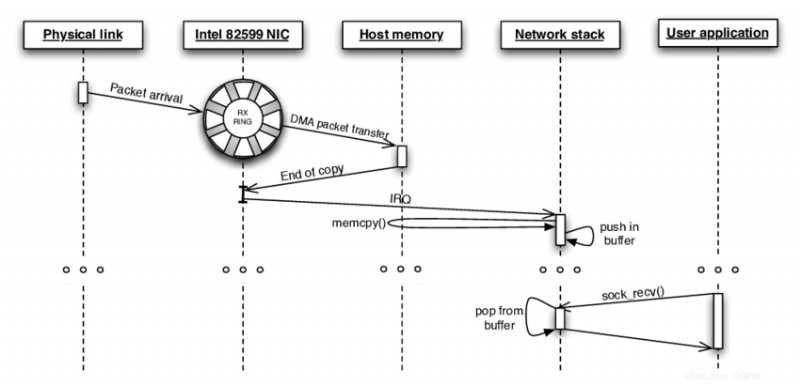

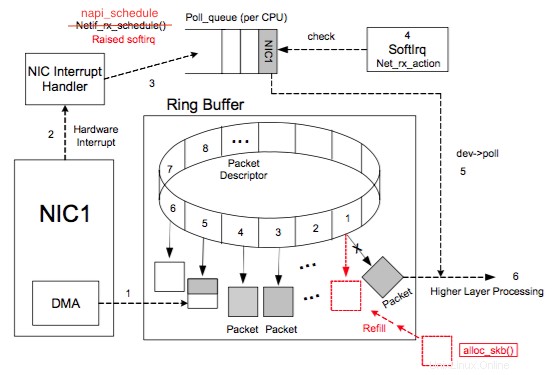

A menudo se ve una variante del enfoque asíncrono con las tarjetas de red. Estas tarjetas a menudo esperan ver un búfer circular (a menudo llamado búfer de anillo DMA) establecido en la memoria compartida con el procesador; cada paquete entrante se coloca en el siguiente búfer disponible en el anillo y se señala una interrupción. Luego, el controlador pasa los paquetes de red al resto del núcleo y coloca un nuevo búfer DMA en el anillo.

El anillo DMA permite que la NIC acceda directamente a la memoria utilizada por el software. El software (el controlador de la NIC en el caso del kernel) asigna memoria para los anillos y luego la mapea como memoria DMA, de modo que la NIC sepa que puede acceder a ella. El software creará los paquetes TX en esta memoria y la NIC los leerá y transmitirá (generalmente después de que el software señale a la NIC que debe comenzar a transmitir). La NIC escribirá los paquetes RX en esta memoria y el software los leerá y procesará (generalmente después de que se emita una interrupción para indicar que hay trabajo).

Espero que esto ayude.

-

El búfer de anillo contiene la dirección inicial y final del búfer en la RAM. El anillo TX contendrá las direcciones del búfer en la RAM que contiene los datos que se transmitirán. El anillo RX contendrá la dirección del búfer en la RAM donde la NIC colocará los datos.

Estos anillos están presentes en la RAM.

-

El búfer de TX y el búfer de RX están en la RAM señalados por anillos de TX/RX.

-

Ahora el registro de la tarjeta de red tiene la ubicación del búfer de anillos en la RAM.

Ahora 1 y 2 pueden ser un búfer compatible con DMA, se llaman anillo DMA TX/RX y búfer DMA TX/RX. Ahora, dado que el anillo RX/TX debe permanecer en todo momento, se hacen como un tipo de memoria DMA consistente/coherente. Mientras se hacen los búferes transmisión/tipo de memoria DMA único